#### POLITECNICO **DI TORINO**

# PhD in Computer and Control Engineering

Guido Marchetto

Advisor

Dipartimento di Automatica e Informatica

XXIX cycle

# Æthereal NoC blocking analysis

PhD Candidate:

#### 1. Networks on Chip?

"Network-on-a-chip (NoC) is a new paradigm for System-on-Chip (SoC) design. NoC based-systems accommodate multiple asynchronous clocking that many of today's complex SoC designs use. The NoC solution brings a networking method to on-chip communications and claims roughly a threefold increase over conventional bus performance systems."

#### 2. Bus vs Networks-on-Chip (NoCs)

# Sarosh Tahir

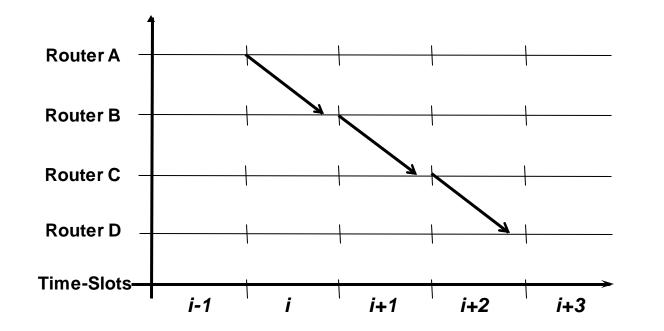

### 6. Forwarding Rules

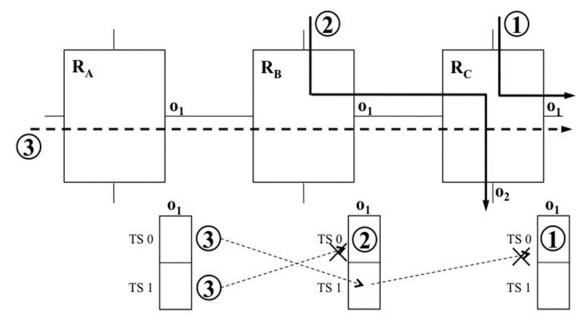

<u>*Rule 1.*</u> A packet *p* transmitted in time-slot *t* by router  $R_k$  must be transmitted in time-slot (t + 1) mod S by router  $R_{k+1}$ .

<u>*Rule 2.*</u> A packet *p* transmitted in time-slot *t* by router  $R_k$  must be transmitted in time-slot (*t*+*d*) mod S, *d* < S by router  $R_{k+1}$ .

#### 7. BLOCKING ANALYSIS

- Unicast traffic, although multicast is supported in Æthereal.

- Poisson distributed GS connection arrivals.

#### **11. Proposed Solution**

<u>*Rule 3.*</u> A packet *p* transmitted in time-slot *t* by router  $R_k$  must be transmitted in time-slot  $(t+d) \mod S, d \leq D$  by router  $R_{k+1}$ .

#### **Bus based** interconnect

- Low cost

- Ease to Implement

- Flexibility

3.

- **Networks on Chip**

- Layered Approach

- Buses replaced with Networked architectures

- Better electrical properties

- Higher bandwidth

- Energy efficiency

- Scalability

- Asynchronous NoCs

**Proposals**

• Pure circuit switching

#### **PHILIPS** proposed to put the two worlds together

- Virtual circuit switching

- share links (and buffers) in time (TDM), e.g. **Æthereal**

- Aethereal network on chip (The Synchronous thing)

- multi-hop interconnect

- timing closure, GALS

- modularity

- guaranteed service (GS)

- real time

- robustness

- best-effort (BE)

- One time-slot per link capacity required by each connection.

- Random selection of time-slots at connection sources.

- Static routing, i.e., no alternative paths can be considered between each source/destination pair.

- Mutual independency of load distributions (i.e., distribution of reserved time-slots) at different links.

- **Un-schedulability** in a simple **Æthereal NoC**

9. blocking probability at the last hop H:  $P_{b}^{(H)} = P^{(H)}(S) = \sum_{i=0}^{S} \sum_{j=0}^{S} P(S|_{i,j}) P^{(H-1)}(j) P_{(j)}$

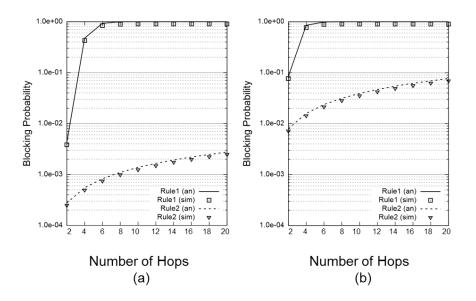

## **10. Blocking Probability**

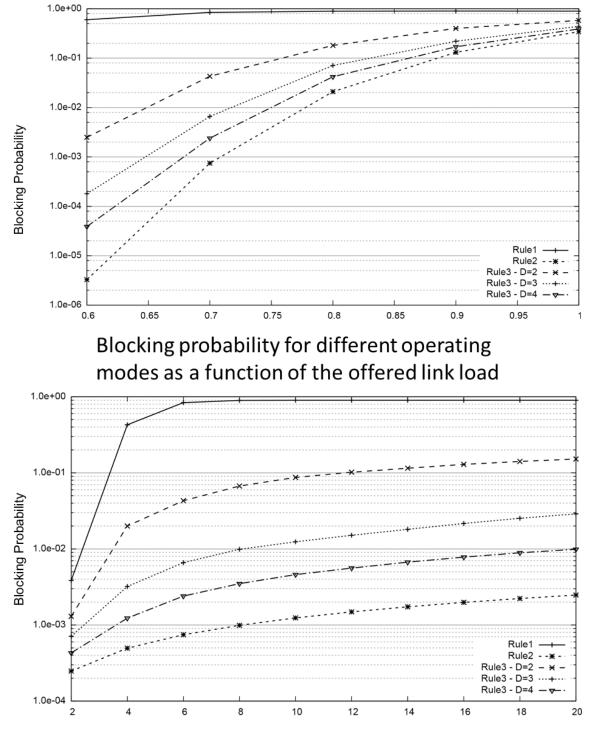

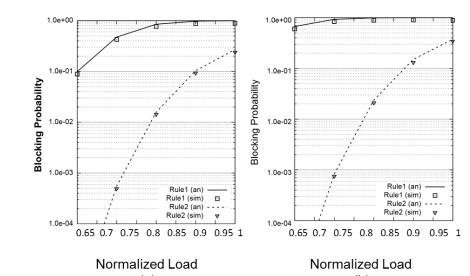

Blocking probability for different operating modes as a function of the path length.

Small increments in buffer size result in a significant reduction of the blocking probability.

#### 12.Conclusions

- Analytical model demonstrates how the blocking probability might be significant if resource reservation is performed at run-time and buffering is minimized

- Simulation shows how the blocking problem can be mitigated by means of small buffer size increments, thus defining a proper Æthereal operating rule that could satisfy both blocking (i.e., resource efficiency) and buffering constraints.

#### 14.Publication

G. Marchetto, S. Tahir, M. Grosso "A Blocking Probability Study for the Aethereal Network-on-Chip", Submitted to IEEE International Design and Test Symposium (IDT 2016)

-low cost

#### automated design flow

- dimensioning, incl. buffer sizing

- performance closure

#### **Æthereal operating principles** 5.

Blocking probability as a function of the offered link load: (a) H = 4; (b) H = 6.

Blocking probability as a function of the path length: (a)  $\rho = 0.7$ ; (b)  $\rho = 0.8$

Æthereal NoC operating according to Rule 2 ensures a blocking probability lower than that obtained when Rule 1 is adopted. However, this operating mode is unfeasible due to its large buffering requirements.

#### 14.References

[1]A. Radulescu, J. Dielissen, S. Pestana, O. Gangwal, E. Rijpkema, P. Wielage, and K. Goossens, "An efficient on-chip NI offering guaranteed services, sharedmemory abstraction, and flexible network configuration," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, vol. 24, no. 1, pp. 4–17, 2005.

[2]A. Hansson, M. Subburaman, and K. Goossens, "Aelite: A flitsynchronous Network on Chip with composable and predictable services," in Proc. of IEEE/ACM Design, Automation Test in Europe Conference Exhibition (DATE 2009)., 2009, pp. 250–255.

[3]K. Goossens and A. Hansson, "The AEthereal network on chip after ten years: Goals, evolution, lessons, and future," in Proceedings of the ACM Design Automation Conference (DAC 2010), 2010, pp. 306–311.

[4]M. Schoeberl, F. Brandner, J. Spars, and E. Kasapaki, "A statically scheduled time-division-multiplexed network-on-chip for real-time systems,' in Networks on Chip (NoCS), 2012 Sixth IEEE/ACM International Symposium on, May 2012, pp. 152–160.

[5]R. Stefan, A. Molnos, and K. Goossens, "daelite: A tdm noc supporting qos, multicast, and fast connection setup," Computers, IEEE Transactions on, vol. 63, no. 3, pp. 583–594, March 2014.

[6]S. Liu, A. Jantsch, and Z. Lu, "Parallel probe based dynamic connection setup in tdm nocs," in Design, Automation and Test in Europe Conference and Exhibition (DATE), 2014, March 2014, pp. 1–6.